Noong 1965, ipinahayag ng co-founder ng Intel na si Gordon Moore ang naging "Moore's Law." Sa loob ng mahigit kalahating siglo, sinuportahan nito ang patuloy na pagtaas ng performance ng integrated-circuit (IC) at pagbaba ng mga gastos—ang pundasyon ng modernong digital na teknolohiya. Sa madaling salita: ang bilang ng mga transistor sa isang chip ay halos dumoble bawat dalawang taon.

Sa loob ng maraming taon, sinundan ng pag-unlad ang ritmo na iyon. Ngayon ay nagbabago na ang sitwasyon. Ang karagdagang pag-urong ay lalong naging mahirap; ang mga laki ng tampok ay bumababa na lamang sa ilang nanometer. Ang mga inhinyero ay nakakaranas ng mga pisikal na limitasyon, mas kumplikadong mga hakbang sa proseso, at tumataas na mga gastos. Ang mas maliliit na heometriya ay nagpapababa rin sa ani, na nagpapahirap sa mataas na dami ng produksyon. Ang pagbuo at pagpapatakbo ng isang nangungunang pabrika ay nangangailangan ng napakalaking kapital at kadalubhasaan. Kaya naman marami ang nangangatwiran na ang Batas ni Moore ay nawawalan ng lakas.

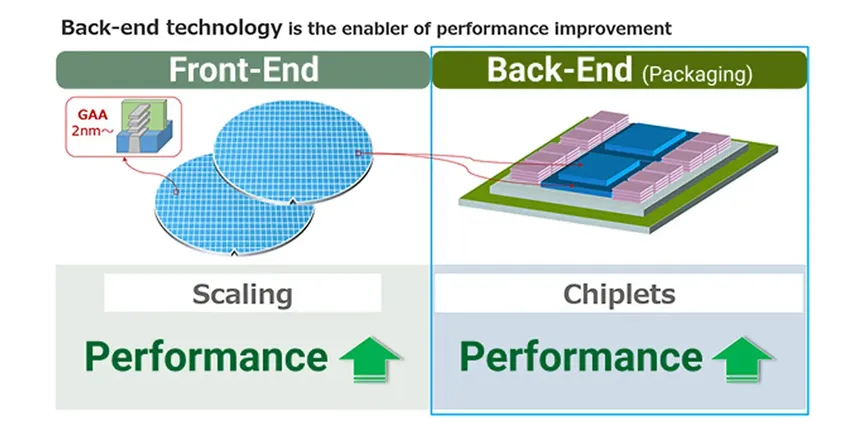

Ang pagbabagong iyon ay nagbukas ng pinto sa isang bagong diskarte: mga chiplet.

Ang chiplet ay isang maliit na die na gumaganap ng isang partikular na tungkulin—isang hiwa ng dating isang monolitikong chip. Sa pamamagitan ng pagsasama ng maraming chiplet sa isang pakete, maaaring bumuo ang mga tagagawa ng isang kumpletong sistema.

Noong panahong monolitiko, lahat ng tungkulin ay nasa iisang malaking die lamang, kaya ang isang depekto kahit saan ay maaaring masira ang buong chip. Sa mga chiplet, ang mga sistema ay binubuo mula sa "known-good die" (KGD), na lubhang nagpapabuti sa ani at kahusayan sa pagmamanupaktura.

Ang heterogeneous integration—ang pagsasama-sama ng mga die na binuo sa iba't ibang process node at para sa iba't ibang function—ay ginagawang lalong makapangyarihan ang mga chiplet. Maaaring gamitin ng mga high-performance compute block ang mga pinakabagong node, habang ang memory at analog circuit ay nananatili sa mga mature at cost-effective na teknolohiya. Ang resulta: mas mataas na performance sa mas mababang gastos.

Partikular na interesado ang industriya ng sasakyan. Ginagamit ng mga pangunahing tagagawa ng sasakyan ang mga pamamaraang ito upang bumuo ng mga in-vehicle SoC sa hinaharap, na may target na malawakang paggamit pagkatapos ng 2030. Pinapayagan sila ng mga chiplet na mapalawak ang AI at graphics nang mas mahusay habang pinapabuti ang ani—na nagpapalakas sa parehong performance at functionality sa mga automotive semiconductor.

Ang ilang piyesa ng sasakyan ay dapat matugunan ang mahigpit na pamantayan sa kaligtasan ng paggana at sa gayon ay umaasa sa mga mas luma at napatunayang mga node. Samantala, ang mga modernong sistema tulad ng advanced driver-assistance (ADAS) at mga software-defined vehicle (SDV) ay nangangailangan ng mas maraming compute. Natutugunan ng mga chiplet ang kakulangang iyon: sa pamamagitan ng pagsasama-sama ng mga safety-class microcontroller, malaking memorya, at malalakas na AI accelerator, maaaring iangkop ng mga tagagawa ang mga SoC sa mga pangangailangan ng bawat automaker—nang mas mabilis.

Ang mga bentaheng ito ay higit pa sa mga sasakyan. Ang mga arkitektura ng chiplet ay kumakalat sa AI, telecom, at iba pang mga larangan, na nagpapabilis sa inobasyon sa iba't ibang industriya at mabilis na nagiging isang haligi ng roadmap ng semiconductor.

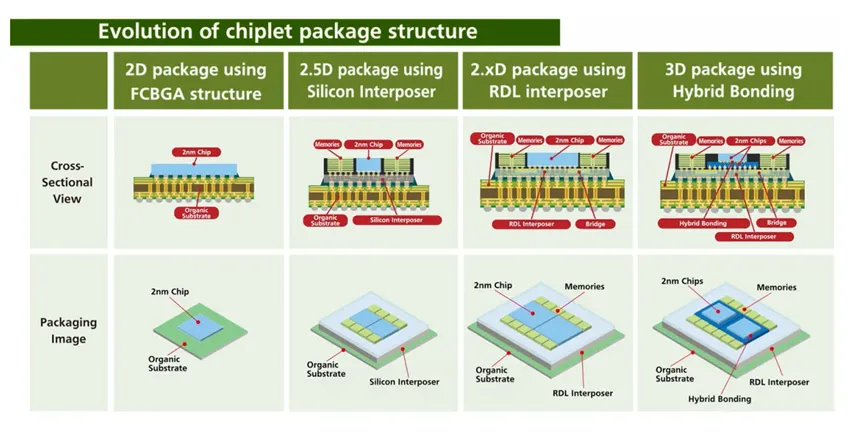

Ang integrasyon ng chiplet ay nakasalalay sa mga siksik at mabilis na koneksyon ng die-to-die. Ang pangunahing tagapagpagana ay ang interposer—isang intermediate layer, kadalasang silicon, sa ilalim ng mga die na nagruruta ng mga signal na parang isang maliit na circuit board. Ang mas mahusay na mga interposer ay nangangahulugan ng mas mahigpit na pagkabit at mas mabilis na pagpapalitan ng signal.

Pinapabuti rin ng advanced packaging ang paghahatid ng kuryente. Ang mga siksik na hanay ng maliliit na koneksyon ng metal sa pagitan ng mga die ay nagbibigay ng sapat na daanan para sa kuryente at data kahit sa masisikip na espasyo, na nagbibigay-daan sa mataas na bandwidth transfer habang ginagamit nang mahusay ang limitadong lugar ng pakete.

Ang pangunahing pamamaraan ngayon ay ang 2.5D integration: ang paglalagay ng maraming die nang magkatabi sa isang interposer. Ang susunod na hakbang ay ang 3D integration, kung saan ang mga die ay pinatong-patong nang patayo gamit ang through-silicon vias (TSVs) para sa mas mataas na densidad.

Ang pagsasama-sama ng modular chip design (paghihiwalay ng mga function at uri ng circuit) at 3D stacking ay nagbubunga ng mas mabilis, mas maliit, at mas matipid sa enerhiya na mga semiconductor. Ang co-locating memory at compute ay naghahatid ng malaking bandwidth sa malalaking dataset—mainam para sa AI at iba pang high-performance workload.

Gayunpaman, ang patayong pagsasalansan ay nagdudulot ng mga hamon. Mas madaling maipon ang init, na nagpapakomplikado sa pamamahala at ani ng init. Upang matugunan ito, isinusulong ng mga mananaliksik ang mga bagong pamamaraan ng pag-iimpake upang mas mahusay na mahawakan ang mga limitasyon sa init. Gayunpaman, malakas ang momentum: ang pagtatagpo ng mga chiplet at 3D integration ay malawakang tinitingnan bilang isang disruptive paradigm—na handang magdala ng sulo kung saan natatapos ang Batas ni Moore.

Oras ng pag-post: Oktubre-15-2025