Kagamitan sa Pagnipis ng Wafer para sa 4 na Pulgada-12 Pulgadang Pagproseso ng Sapphire/SiC/Si Wafers

Prinsipyo ng Paggawa

Ang proseso ng paggawa ng manipis na wafer ay isinasagawa sa tatlong yugto:

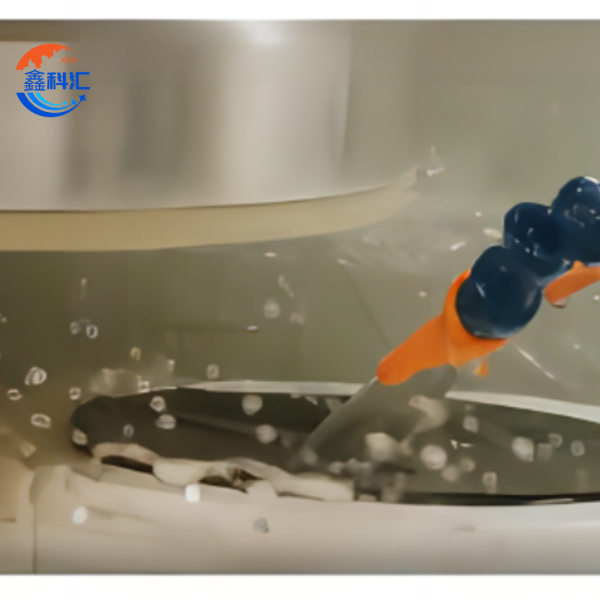

Magaspang na Paggiling: Ang isang diamond wheel (laki ng grit na 200–500 μm) ay nag-aalis ng 50–150 μm ng materyal sa 3000–5000 rpm upang mabilis na mabawasan ang kapal.

Pinong Paggiling: Ang mas pinong gulong (laki ng grit na 1–50 μm) ay nagbabawas ng kapal sa 20–50 μm sa <1 μm/s upang mabawasan ang pinsala sa ilalim ng lupa.

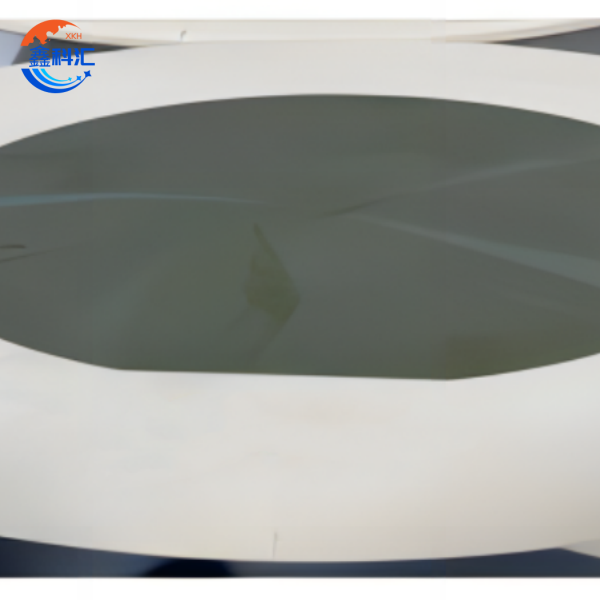

Pagpapakintab (CMP): Ang isang kemikal-mekanikal na slurry ay nag-aalis ng natitirang pinsala, na nakakamit ng Ra <0.1 nm.

Mga Katugmang Materyales

Silikon (Si): Pamantayan para sa mga CMOS wafer, pinanipis sa 25 μm para sa 3D stacking.

Silicon Carbide (SiC): Nangangailangan ng espesyal na mga gulong na diamante (80% konsentrasyon ng diamante) para sa thermal stability.

Sapphire (Al₂O₃): Ninipis hanggang 50 μm para sa mga aplikasyon ng UV LED.

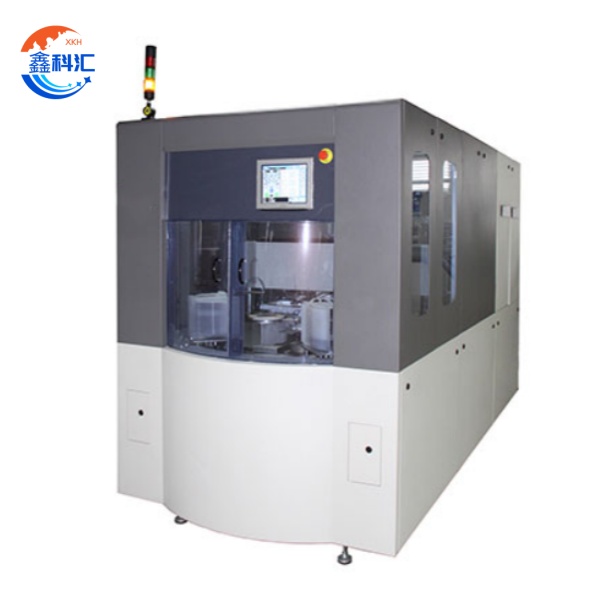

Mga Pangunahing Bahagi ng Sistema

1. Sistema ng Paggiling

Dual-Axis Grinder: Pinagsasama ang magaspang/pinong paggiling sa iisang plataporma, na binabawasan ang oras ng pag-ikot ng 40%.

Aerostatic Spindle: Saklaw ng bilis na 0–6000 rpm na may <0.5 μm radial runout.

2. Sistema ng Paghawak ng Wafer

Vacuum Chuck: >50 N na puwersa ng paghawak na may ±0.1 μm na katumpakan sa pagpoposisyon.

Robotic Arm: Naghahatid ng 4–12-pulgadang wafer sa bilis na 100 mm/s.

3. Sistema ng Kontrol

Laser Interferometry: Pagsubaybay sa kapal sa totoong oras (resolusyon na 0.01 μm).

AI-Driven Feedforward: Hinuhulaan ang pagkasira ng gulong at awtomatikong inaayos ang mga parameter.

4. Pagpapalamig at Paglilinis

Paglilinis ng Ultrasonic: Tinatanggal ang mga particle na >0.5 μm na may 99.9% na kahusayan.

Deionized na Tubig: Pinapalamig ang wafer sa <5°C na mas mataas kaysa sa ambient.

Mga Pangunahing Kalamangan

1. Ultra-High Precision: TTV (Kabuuang Pagkakaiba-iba ng Kapal) <0.5 μm, WTW (Pagkakaiba-iba ng Kapal sa Loob ng Wafer) <1 μm.

2. Pagsasama ng Maramihang Proseso: Pinagsasama ang paggiling, CMP, at plasma etching sa iisang makina.

3. Pagkakatugma ng Materyal:

Silikon: Pagbabawas ng kapal mula 775 μm hanggang 25 μm.

SiC: Nakakamit ng <2 μm TTV para sa mga aplikasyon ng RF.

Mga Doped Wafer: Mga InP wafer na may doped na phosphorus na may <5% resistivity drift.

4. Smart Automation: Binabawasan ng integrasyon ng MES ang pagkakamali ng tao nang 70%.

5. Kahusayan sa Enerhiya: 30% na mas mababang konsumo ng kuryente sa pamamagitan ng regenerative braking.

Mga Pangunahing Aplikasyon

1. Makabagong Pagbalot

• Mga 3D IC: Ang wafer thinning ay nagbibigay-daan sa patayong pagsasalansan ng mga logic/memory chip (hal., mga HBM stack), na nakakamit ng 10× na mas mataas na bandwidth at 50% na nabawasang pagkonsumo ng kuryente kumpara sa mga 2.5D na solusyon. Sinusuportahan ng kagamitan ang hybrid bonding at TSV (Through-Silicon Via) integration, na mahalaga para sa mga AI/ML processor na nangangailangan ng <10 μm interconnect pitch. Halimbawa, ang 12-inch wafers na pinanipis sa 25 μm ay nagbibigay-daan sa pagsasalansan ng 8+ layer habang pinapanatili ang <1.5% warpage, na mahalaga para sa mga automotive LiDAR system.

• Fan-Out Packaging: Sa pamamagitan ng pagbabawas ng kapal ng wafer sa 30 μm, ang haba ng interconnect ay naiikli ng 50%, na nagpapaliit sa signal delay (<0.2 ps/mm) at nagbibigay-daan sa 0.4 mm ultra-thin chiplets para sa mga mobile SoC. Ginagamit ng proseso ang mga stress-compensated grinding algorithm upang maiwasan ang warpage (>50 μm TTV control), na tinitiyak ang pagiging maaasahan sa mga high-frequency RF application.

2. Elektroniks ng Enerhiya

• Mga IGBT Module: Ang pagnipis hanggang 50 μm ay nakakabawas sa thermal resistance sa <0.5°C/W, na nagbibigay-daan sa 1200V SiC MOSFET na gumana sa 200°C na temperatura ng junction. Ang aming kagamitan ay gumagamit ng multi-stage grinding (magaspang: 46 μm grit → pino: 4 μm grit) upang maalis ang pinsala sa ilalim ng lupa, na nakakamit ng >10,000 cycle ng thermal cycling reliability. Ito ay kritikal para sa mga EV inverter, kung saan ang 10 μm-thick SiC wafers ay nagpapabuti sa bilis ng paglipat ng 30%.

• Mga Kagamitang Pangkapangyarihan ng GaN-on-SiC: Ang pagpapanipis ng wafer hanggang 80 μm ay nagpapahusay sa electron mobility (μ > 2000 cm²/V·s) para sa 650V GaN HEMTs, na binabawasan ang conduction losses ng 18%. Ang proseso ay gumagamit ng laser-assisted dicing upang maiwasan ang pagbibitak habang nagpapanipis, na nakakamit ng <5 μm edge chipping para sa mga RF power amplifier.

3. Optoelektronika

• Mga GaN-on-SiC LED: Pinapabuti ng 50 μm sapphire substrates ang light extraction efficiency (LEE) sa 85% (kumpara sa 65% para sa 150 μm wafers) sa pamamagitan ng pagliit ng photon trapping. Tinitiyak ng ultra-low TTV control (<0.3 μm) ng aming kagamitan ang pare-parehong LED emission sa mga 12-inch wafer, na mahalaga para sa mga Micro-LED display na nangangailangan ng <100nm wavelength uniformity.

• Silicon Photonics: Ang mga silicon wafer na may kapal na 25μm ay nagbibigay-daan sa 3 dB/cm na mas mababang propagation loss sa mga waveguide, na mahalaga para sa 1.6 Tbps optical transceiver. Isinasama ng proseso ang CMP smoothing upang mabawasan ang surface roughness sa Ra <0.1 nm, na nagpapahusay sa coupling efficiency ng 40%.

4. Mga Sensor ng MEMS

• Mga Accelerometer: Ang 25 μm silicon wafers ay nakakamit ng SNR na >85 dB (kumpara sa 75 dB para sa 50 μm wafers) sa pamamagitan ng pagpapataas ng sensitivity ng proof-mass displacement. Ang aming dual-axis grinding system ay bumabawi sa mga stress gradient, na tinitiyak ang <0.5% sensitivity drift sa -40°C hanggang 125°C. Kabilang sa mga aplikasyon ang automotive crash detection at AR/VR motion tracking.

• Mga Sensor ng Presyon: Ang pagnipis sa 40 μm ay nagbibigay-daan sa mga saklaw ng pagsukat na 0–300 bar na may <0.1% FS hysteresis. Gamit ang pansamantalang pagbubuklod (mga tagapagdala ng salamin), naiiwasan ng proseso ang pagkabali ng wafer habang nag-uukit sa likuran, na nakakamit ng <1 μm na tolerance sa overpressure para sa mga industrial IoT sensor.

• Teknikal na Sinergy: Pinagsasama ng aming kagamitan sa paggawa ng manipis na wafer ang mechanical grinding, CMP, at plasma etching upang matugunan ang magkakaibang hamon sa materyal (Si, SiC, Sapphire). Halimbawa, ang GaN-on-SiC ay nangangailangan ng hybrid grinding (diamond wheels + plasma) upang balansehin ang katigasan at thermal expansion, habang ang mga MEMS sensor ay nangangailangan ng sub-5 nm surface roughness sa pamamagitan ng CMP polishing.

• Epekto sa Industriya: Sa pamamagitan ng pagpapagana ng mas manipis at mas mataas na performance na mga wafer, ang teknolohiyang ito ay nagtutulak ng mga inobasyon sa mga AI chip, 5G mmWave module, at flexible electronics, na may mga TTV tolerance na <0.1 μm para sa mga foldable display at <0.5 μm para sa mga automotive LiDAR sensor.

Mga Serbisyo ng XKH

1. Mga Pasadyang Solusyon

Mga Nasusukat na Konpigurasyon: Mga disenyo ng silid na may 4–12-pulgadang may awtomatikong pagkarga/pagbaba.

Suporta sa Doping: Mga pasadyang recipe para sa mga kristal na may doping na Er/Yb at mga wafer na InP/GaAs.

2. Suporta mula sa Dulo hanggang Dulo

Pag-unlad ng Proseso: Libreng pagsubok na may kasamang pag-optimize.

Pandaigdigang Pagsasanay: Mga teknikal na workshop taun-taon tungkol sa pagpapanatili at pag-troubleshoot.

3. Pagproseso ng Maraming Materyal

SiC: Pagnipis ng wafer hanggang 100 μm na may Ra <0.1 nm.

Sapiro: 50μm kapal para sa mga bintana ng UV laser (transmittance >92%@200 nm).

4. Mga Serbisyong Nagdaragdag ng Halaga

Suplay na Pangkonsumo: Mga gulong na diamante (2000+ wafer/buhay) at mga CMP slurry.

Konklusyon

Ang kagamitang ito para sa pagnipis ng wafer ay naghahatid ng nangunguna sa industriya na katumpakan, versatility sa maraming materyal, at matalinong automation, kaya naman kailangan ito para sa 3D integration at power electronics. Tinitiyak ng komprehensibong serbisyo ng XKH—mula sa pagpapasadya hanggang sa post-processing—na nakakamit ng mga kliyente ang kahusayan sa gastos at kahusayan sa pagganap sa paggawa ng semiconductor.