Abstrak ng SiC wafer

Mga wafer na silicon carbide (SiC)ay naging substrate ng pagpili para sa mga high-power, high-frequency, at high-temperature electronics sa mga sektor ng automotive, renewable energy, at aerospace. Sakop ng aming portfolio ang mga pangunahing polytype at doping scheme—nitrogen-doped 4H (4H-N), high-purity semi-insulating (HPSI), nitrogen-doped 3C (3C-N), at p-type 4H/6H (4H/6H-P)—na inaalok sa tatlong grado ng kalidad: PRIME (ganap na pinakintab, device-grade substrates), DUMMY (na-lapped o hindi pinakintab para sa mga pagsubok sa proseso), at RESEARCH (mga custom epi layer at doping profile para sa R&D). Ang mga diametro ng wafer ay sumasaklaw sa 2″, 4″, 6″, 8″, at 12″ upang umangkop sa parehong mga legacy tool at advanced na fab. Nagbibigay din kami ng mga monocrystalline boule at mga precision oriented seed crystal upang suportahan ang in-house crystal growth.

Ang aming 4H-N wafers ay nagtatampok ng mga carrier density mula 1×10¹⁶ hanggang 1×10¹⁹ cm⁻³ at resistivities na 0.01–10 Ω·cm, na naghahatid ng mahusay na electron mobility at breakdown fields na higit sa 2 MV/cm—mainam para sa mga Schottky diode, MOSFET, at JFET. Ang mga HPSI substrates ay lumalagpas sa 1×10¹² Ω·cm resistivity na may mga micropipe density na mas mababa sa 0.1 cm⁻², na tinitiyak ang minimal na leakage para sa mga RF at microwave device. Ang Cubic 3C-N, na makukuha sa 2″ at 4″ na format, ay nagbibigay-daan sa heteroepitaxy sa silicon at sumusuporta sa mga nobelang photonic at MEMS applications. Ang mga P-type 4H/6H-P wafers, na nilagyan ng aluminum hanggang 1×10¹⁶–5×10¹⁸ cm⁻³, ay nagpapadali sa mga komplementaryong arkitektura ng device.

Ang mga SiC wafer at PRIME wafer ay sumasailalim sa kemikal-mekanikal na pagpapakintab hanggang sa <0.2 nm RMS surface roughness, kabuuang kapal na pagkakaiba-iba sa ilalim ng 3 µm, at bow na <10 µm. Pinabibilis ng mga DUMMY substrate ang mga pagsubok sa pag-assemble at packaging, habang ang mga RESEARCH wafer ay nagtatampok ng mga epi-layer na kapal na 2–30 µm at bespoke doping. Ang lahat ng produkto ay sertipikado ng X-ray diffraction (rocking curve <30 arcsec) at Raman spectroscopy, na may mga electrical test—Hall measurements, C–V profiling, at micropipe scanning—na tinitiyak ang pagsunod sa JEDEC at SEMI.

Ang mga boule na hanggang 150 mm ang diyametro ay pinapatubo sa pamamagitan ng PVT at CVD na may dislocation densities na mas mababa sa 1×10³ cm⁻² at mababang bilang ng micropipe. Ang mga kristal ng binhi ay pinuputol sa loob ng 0.1° ng c-axis upang matiyak ang maaaring kopyahing paglaki at mataas na ani sa paghiwa.

Sa pamamagitan ng pagsasama-sama ng maraming polytype, mga variant ng doping, mga grado ng kalidad, mga laki ng SiC wafer, at in-house na produksyon ng boule at seed-crystal, pinapadali ng aming SiC substrate platform ang mga supply chain at pinapabilis ang pagbuo ng device para sa mga electric vehicle, smart grid, at mga aplikasyon na lumalaban sa malupit na kapaligiran.

Abstrak ng SiC wafer

Mga wafer na silicon carbide (SiC)ay naging SiC substrate na pinipili para sa mga high-power, high-frequency, at high-temperature electronics sa mga sektor ng automotive, renewable energy, at aerospace. Sinasaklaw ng aming portfolio ang mga pangunahing polytype at doping scheme—nitrogen-doped 4H (4H-N), high-purity semi-insulating (HPSI), nitrogen-doped 3C (3C-N), at p-type 4H/6H (4H/6H-P)—na inaalok sa tatlong grado ng kalidad: SiC waferPRIME (ganap na pinakintab, mga substrate na pang-device), DUMMY (na-lapped o hindi pinakintab para sa mga pagsubok sa proseso), at RESEARCH (mga custom na epi layer at doping profile para sa R&D). Ang mga diyametro ng SiC Wafer ay sumasaklaw sa 2″, 4″, 6″, 8″, at 12″ upang umangkop sa parehong mga legacy tool at advanced na fab. Nagbibigay din kami ng mga monocrystalline boule at mga precision oriented seed crystal upang suportahan ang in-house crystal growth.

Ang aming 4H-N SiC wafers ay nagtatampok ng mga carrier density mula 1×10¹⁶ hanggang 1×10¹⁹ cm⁻³ at resistivities na 0.01–10 Ω·cm, na naghahatid ng mahusay na electron mobility at breakdown fields na higit sa 2 MV/cm—mainam para sa mga Schottky diode, MOSFET, at JFET. Ang mga HPSI substrates ay lumalagpas sa 1×10¹² Ω·cm resistivity na may mga micropipe density na mas mababa sa 0.1 cm⁻², na tinitiyak ang minimal na leakage para sa mga RF at microwave device. Ang Cubic 3C-N, na makukuha sa 2″ at 4″ na format, ay nagbibigay-daan sa heteroepitaxy sa silicon at sumusuporta sa mga nobelang photonic at MEMS applications. Ang SiC wafer P-type 4H/6H-P wafers, na nilagyan ng aluminum hanggang 1×10¹⁶–5×10¹⁸ cm⁻³, ay nagpapadali sa mga komplementaryong arkitektura ng device.

Ang mga SiC wafer PRIME wafer ay sumasailalim sa kemikal-mekanikal na pagpapakintab hanggang sa <0.2 nm RMS surface roughness, kabuuang kapal na pagkakaiba-iba sa ilalim ng 3 µm, at bow na <10 µm. Pinabibilis ng mga DUMMY substrate ang mga pagsubok sa pag-assemble at packaging, habang ang mga RESEARCH wafer ay nagtatampok ng mga epi-layer na kapal na 2–30 µm at bespoke doping. Ang lahat ng produkto ay sertipikado ng X-ray diffraction (rocking curve <30 arcsec) at Raman spectroscopy, na may mga electrical test—Hall measurements, C–V profiling, at micropipe scanning—na tinitiyak ang pagsunod sa JEDEC at SEMI.

Ang mga boule na hanggang 150 mm ang diyametro ay pinapatubo sa pamamagitan ng PVT at CVD na may dislocation densities na mas mababa sa 1×10³ cm⁻² at mababang bilang ng micropipe. Ang mga kristal ng binhi ay pinuputol sa loob ng 0.1° ng c-axis upang matiyak ang maaaring kopyahing paglaki at mataas na ani sa paghiwa.

Sa pamamagitan ng pagsasama-sama ng maraming polytype, mga variant ng doping, mga grado ng kalidad, mga laki ng SiC wafer, at in-house na produksyon ng boule at seed-crystal, pinapadali ng aming SiC substrate platform ang mga supply chain at pinapabilis ang pagbuo ng device para sa mga electric vehicle, smart grid, at mga aplikasyon na lumalaban sa malupit na kapaligiran.

Data sheet ng 6 na pulgadang 4H-N type SiC wafer

| 6 na pulgadang SiC wafers data sheet | ||||

| Parametro | Sub-Parameter | Baitang Z | Grado P | Baitang D |

| Diyametro | 149.5–150.0 mm | 149.5–150.0 mm | 149.5–150.0 mm | |

| Kapal | 4H-N | 350 µm ± 15 µm | 350 µm ± 25 µm | 350 µm ± 25 µm |

| Kapal | 4H-SI | 500 µm ± 15 µm | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Oryentasyon ng Wafer | Malayo sa aksis: 4.0° patungo sa <11-20> ±0.5° (4H-N); Nasa aksis: <0001> ±0.5° (4H-SI) | Malayo sa aksis: 4.0° patungo sa <11-20> ±0.5° (4H-N); Nasa aksis: <0001> ±0.5° (4H-SI) | Malayo sa aksis: 4.0° patungo sa <11-20> ±0.5° (4H-N); Nasa aksis: <0001> ±0.5° (4H-SI) | |

| Densidad ng Mikropipe | 4H-N | ≤ 0.2 cm⁻² | ≤ 2 cm⁻² | ≤ 15 cm⁻² |

| Densidad ng Mikropipe | 4H-SI | ≤ 1 cm⁻² | ≤ 5 cm⁻² | ≤ 15 cm⁻² |

| Resistivity | 4H-N | 0.015–0.024 Ω·cm | 0.015–0.028 Ω·cm | 0.015–0.028 Ω·cm |

| Resistivity | 4H-SI | ≥ 1×10¹⁰ Ω·cm | ≥ 1×10⁵ Ω·cm | |

| Pangunahing Patag na Oryentasyon | [10-10] ± 5.0° | [10-10] ± 5.0° | [10-10] ± 5.0° | |

| Pangunahing Patag na Haba | 4H-N | 47.5 mm ± 2.0 mm | ||

| Pangunahing Patag na Haba | 4H-SI | bingaw | ||

| Pagbubukod sa Gilid | 3 milimetro | |||

| Warp/LTV/TTV/Pana | ≤2.5 µm / ≤6 µm / ≤25 µm / ≤35 µm | ≤5 µm / ≤15 µm / ≤40 µm / ≤60 µm | ||

| Kagaspangan | Polish | Ra ≤ 1 nm | ||

| Kagaspangan | CMP | Ra ≤ 0.2 nm | Ra ≤ 0.5 nm | |

| Mga Bitak sa Gilid | Wala | Pinagsama-samang haba ≤ 20 mm, isahan ≤ 2 mm | ||

| Mga Platong Heksagonal | Pinagsama-samang lawak ≤ 0.05% | Pinagsama-samang lawak ≤ 0.1% | Pinagsama-samang lawak ≤ 1% | |

| Mga Lugar na Polytype | Wala | Pinagsama-samang lawak ≤ 3% | Pinagsama-samang lawak ≤ 3% | |

| Mga Pagsasama ng Carbon | Pinagsama-samang lawak ≤ 0.05% | Pinagsama-samang lawak ≤ 3% | ||

| Mga Gasgas sa Ibabaw | Wala | Pinagsama-samang haba ≤ 1 × diyametro ng wafer | ||

| Mga Edge Chips | Walang pinapayagang lapad at lalim na ≥ 0.2 mm | Hanggang 7 chips, ≤ 1 mm bawat isa | ||

| TSD (Paglinsad ng Turnilyo sa Pag-thread) | ≤ 500 sentimetro⁻² | Wala | ||

| BPD (Dislokasyon ng Base Plane) | ≤ 1000 cm⁻² | Wala | ||

| Kontaminasyon sa Ibabaw | Wala | |||

| Pagbabalot | Multi-wafer cassette o lalagyan ng iisang wafer | Multi-wafer cassette o lalagyan ng iisang wafer | Multi-wafer cassette o lalagyan ng iisang wafer | |

Data sheet ng 4 na pulgadang 4H-N type na SiC wafer

| Data sheet ng 4-pulgadang SiC wafer | |||

| Parametro | Zero MPD Production | Pamantayang Baitang ng Produksyon (Baitang P) | Gradong Dummy (Gradong D) |

| Diyametro | 99.5 mm–100.0 mm | ||

| Kapal (4H-N) | 350 µm±15 µm | 350 µm±25 µm | |

| Kapal (4H-Si) | 500 µm±15 µm | 500 µm±25 µm | |

| Oryentasyon ng Wafer | Malayo sa aksis: 4.0° patungo sa <1120> ±0.5° para sa 4H-N; Nasa aksis: <0001> ±0.5° para sa 4H-Si | ||

| Densidad ng Mikropipe (4H-N) | ≤0.2 cm⁻² | ≤2 cm⁻² | ≤15 cm⁻² |

| Densidad ng Mikropipe (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistivity (4H-N) | 0.015–0.024 Ω·cm | 0.015–0.028 Ω·cm | |

| Resistivity (4H-Si) | ≥1E10 Ω·cm | ≥1E5 Ω·cm | |

| Pangunahing Patag na Oryentasyon | [10-10] ±5.0° | ||

| Pangunahing Patag na Haba | 32.5 mm ±2.0 mm | ||

| Pangalawang Patag na Haba | 18.0 mm ±2.0 mm | ||

| Pangalawang Patag na Oryentasyon | Nakaharap ang silicon: 90° CW mula sa prime flat ±5.0° | ||

| Pagbubukod sa Gilid | 3 milimetro | ||

| LTV/TTV/Pag-ukit ng Pana | ≤2.5 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Kagaspangan | Polish Ra ≤1 nm; CMP Ra ≤0.2 nm | Ra ≤0.5 nm | |

| Mga Bitak sa Gilid Dahil sa Mataas na Intensidad ng Liwanag | Wala | Wala | Pinagsama-samang haba ≤10 mm; iisang haba ≤2 mm |

| Mga Plate na Hex Gamit ang Mataas na Intensity na Liwanag | Pinagsama-samang lawak ≤0.05% | Pinagsama-samang lawak ≤0.05% | Pinagsama-samang lawak ≤0.1% |

| Mga Lugar na Polytype Gamit ang Mataas na Intensity na Liwanag | Wala | Pinagsama-samang lawak ≤3% | |

| Mga Kasamang Biswal na Carbon | Pinagsama-samang lawak ≤0.05% | Pinagsama-samang lawak ≤3% | |

| Mga Gasgas sa Ibabaw ng Silicon Dahil sa Mataas na Intensity na Liwanag | Wala | Pinagsama-samang haba ≤1 diyametro ng wafer | |

| Mga Edge Chips Gamit ang High Intensity Light | Walang pinapayagang lapad at lalim na ≥0.2 mm | 5 pinapayagan, ≤1 mm bawat isa | |

| Kontaminasyon sa Ibabaw ng Silicon Mula sa Mataas na Intensity na Liwanag | Wala | ||

| Dislokasyon ng turnilyo sa pag-thread | ≤500 cm⁻² | Wala | |

| Pagbabalot | Multi-wafer cassette o lalagyan ng iisang wafer | Multi-wafer cassette o lalagyan ng iisang wafer | Multi-wafer cassette o lalagyan ng iisang wafer |

Data sheet ng 4 na pulgadang HPSI type SiC wafer

| Data sheet ng 4 na pulgadang HPSI type SiC wafer | |||

| Parametro | Zero MPD Production Grade (Z Grade) | Pamantayang Baitang ng Produksyon (Baitang P) | Gradong Dummy (Gradong D) |

| Diyametro | 99.5–100.0 mm | ||

| Kapal (4H-Si) | 500 µm ±20 µm | 500 µm ±25 µm | |

| Oryentasyon ng Wafer | Malayo sa aksis: 4.0° patungo sa <11-20> ±0.5° para sa 4H-N; Nasa aksis: <0001> ±0.5° para sa 4H-Si | ||

| Densidad ng Mikropipe (4H-Si) | ≤1 cm⁻² | ≤5 cm⁻² | ≤15 cm⁻² |

| Resistivity (4H-Si) | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |

| Pangunahing Patag na Oryentasyon | (10-10) ±5.0° | ||

| Pangunahing Patag na Haba | 32.5 mm ±2.0 mm | ||

| Pangalawang Patag na Haba | 18.0 mm ±2.0 mm | ||

| Pangalawang Patag na Oryentasyon | Nakaharap ang silicon: 90° CW mula sa prime flat ±5.0° | ||

| Pagbubukod sa Gilid | 3 milimetro | ||

| LTV/TTV/Pag-ukit ng Pana | ≤3 µm/≤5 µm/≤15 µm/≤30 µm | ≤10 µm/≤15 µm/≤25 µm/≤40 µm | |

| Kagaspangan (C na mukha) | Polish | Ra ≤1 nm | |

| Kagaspangan (mukha ni Si) | CMP | Ra ≤0.2 nm | Ra ≤0.5 nm |

| Mga Bitak sa Gilid Dahil sa Mataas na Intensidad ng Liwanag | Wala | Pinagsama-samang haba ≤10 mm; iisang haba ≤2 mm | |

| Mga Plate na Hex Gamit ang Mataas na Intensity na Liwanag | Pinagsama-samang lawak ≤0.05% | Pinagsama-samang lawak ≤0.05% | Pinagsama-samang lawak ≤0.1% |

| Mga Lugar na Polytype Gamit ang Mataas na Intensity na Liwanag | Wala | Pinagsama-samang lawak ≤3% | |

| Mga Kasamang Biswal na Carbon | Pinagsama-samang lawak ≤0.05% | Pinagsama-samang lawak ≤3% | |

| Mga Gasgas sa Ibabaw ng Silicon Dahil sa Mataas na Intensity na Liwanag | Wala | Pinagsama-samang haba ≤1 diyametro ng wafer | |

| Mga Edge Chips Gamit ang High Intensity Light | Walang pinapayagang lapad at lalim na ≥0.2 mm | 5 pinapayagan, ≤1 mm bawat isa | |

| Kontaminasyon sa Ibabaw ng Silicon Mula sa Mataas na Intensity na Liwanag | Wala | Wala | |

| Paglinsad ng Turnilyo sa Pag-thread | ≤500 cm⁻² | Wala | |

| Pagbabalot | Multi-wafer cassette o lalagyan ng iisang wafer | ||

Aplikasyon ng SiC wafer

-

Mga SiC Wafer Power Module para sa mga EV Inverter

Ang mga SiC wafer-based MOSFET at diode na gawa sa mataas na kalidad na SiC wafer substrates ay naghahatid ng napakababang switching losses. Sa pamamagitan ng paggamit ng teknolohiya ng SiC wafer, ang mga power module na ito ay gumagana sa mas mataas na boltahe at temperatura, na nagbibigay-daan sa mas mahusay na mga traction inverter. Ang pagsasama ng mga SiC wafer die sa mga power stage ay nakakabawas sa mga kinakailangan sa paglamig at footprint, na nagpapakita ng buong potensyal ng inobasyon ng SiC wafer. -

Mga High-Frequency RF at 5G Device sa SiC Wafer

Ang mga RF amplifier at switch na ginawa sa mga semi-insulating SiC wafer platform ay nagpapakita ng superior thermal conductivity at breakdown voltage. Binabawasan ng SiC wafer substrate ang dielectric losses sa GHz frequencies, habang ang lakas ng materyal ng SiC wafer ay nagbibigay-daan para sa matatag na operasyon sa ilalim ng mga kondisyon na may mataas na power at mataas na temperatura—na ginagawang substrate ng pagpili ang SiC wafer para sa mga susunod na henerasyon ng 5G base station at radar system. -

Mga Optoelectronic at LED Substrate mula sa SiC Wafer

Ang mga asul at UV LED na itinatanim sa mga substrate ng SiC wafer ay nakikinabang mula sa mahusay na pagtutugma ng lattice at pagpapakalat ng init. Ang paggamit ng pinakintab na C-face SiC wafer ay nagsisiguro ng pantay na mga epitaxial layer, habang ang likas na katigasan ng SiC wafer ay nagbibigay-daan sa pagnipis ng pinong wafer at maaasahang packaging ng device. Ginagawa nitong go-to platform ang SiC wafer para sa mga high-power, long-lifetime na aplikasyon ng LED.

Tanong at Sagot ng SiC wafer

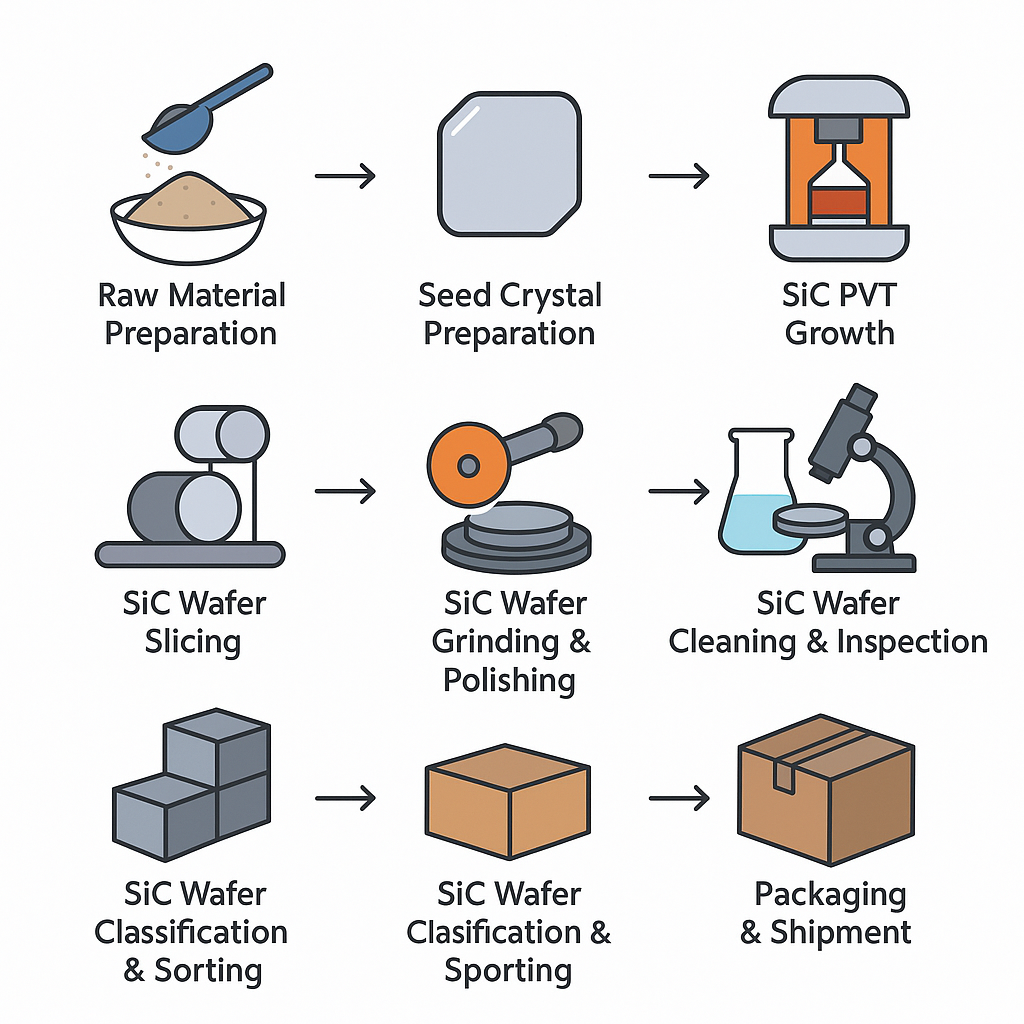

1. T: Paano ginagawa ang mga SiC wafer?

A:

Mga SiC wafer na ginawaMga Detalyadong Hakbang

-

Mga wafer na SiCPaghahanda ng Hilaw na Materyales

- Gumamit ng ≥5N-grade SiC powder (mga dumi ≤1 ppm).

- Salain at i-bake muna upang maalis ang mga natitirang carbon o nitrogen compound.

-

SiCPaghahanda ng Kristal ng Binhi

-

Kumuha ng isang piraso ng 4H-SiC single crystal, hiwain sa oryentasyong 〈0001〉 hanggang ~10 × 10 mm².

-

Pakinisin nang may katumpakan hanggang Ra ≤0.1 nm at markahan ang oryentasyon ng kristal.

-

-

SiCPaglago ng PVT (Pisikal na Transportasyon ng Singaw)

-

Maglagay ng graphite crucible: lagyan ng SiC powder sa ilalim, at lagyan ng seed crystal sa ibabaw.

-

Ilikas hanggang sa 10⁻³–10⁻⁵ Torr o punuin ng high-purity helium sa 1 atm.

-

Painitin ang source zone sa 2100–2300 ℃, panatilihing mas malamig ang seed zone sa 100–150 ℃.

-

Kontrolin ang bilis ng paglaki sa 1–5 mm/h upang balansehin ang kalidad at throughput.

-

-

SiCPag-init ng Ingot

-

I-anneal ang lumaking SiC ingot sa 1600–1800 ℃ sa loob ng 4–8 oras.

-

Layunin: mapawi ang mga thermal stress at mabawasan ang densidad ng dislokasyon.

-

-

SiCPaghiwa ng Wafer

-

Gumamit ng diamond wire saw para hiwain ang ingot sa mga wafer na may kapal na 0.5–1 mm.

-

Bawasan ang panginginig ng boses at puwersa sa gilid upang maiwasan ang maliliit na bitak.

-

-

SiCWaferPaggiling at Pagpapakintab

-

Magaspang na paggilingupang alisin ang pinsala dahil sa paglalagari (kagaspangan ~10–30 µm).

-

Pinong paggilingupang makamit ang patag na ≤5 µm.

-

Kemikal-Mekanikal na Pagpapakintab (CMP)upang maabot ang mala-salamin na wakas (Ra ≤0.2 nm).

-

-

SiCWaferPaglilinis at Inspeksyon

-

Paglilinis gamit ang ultrasonikosa Piranha solution (H₂SO₄:H₂O₂), DI water, pagkatapos ay IPA.

-

Ispektroskopiya ng XRD/Ramanupang kumpirmahin ang polytype (4H, 6H, 3C).

-

Interferometriyaupang sukatin ang kapatagan (<5 µm) at kurba (<20 µm).

-

Apat na puntong probeupang subukan ang resistivity (hal. HPSI ≥10⁹ Ω·cm).

-

Inspeksyon ng depektosa ilalim ng polarized light microscope at scratch tester.

-

-

SiCWaferPag-uuri at Pag-uuri

-

Pagbukud-bukurin ang mga wafer ayon sa polytype at electrical type:

-

4H-SiC N-type (4H-N): konsentrasyon ng carrier 10¹⁶–10¹⁸ cm⁻³

-

4H-SiC Mataas na Kadalisayan na Semi-Insulating (4H-HPSI): resistivity ≥10⁹ Ω·cm

-

6H-SiC N-uri (6H-N)

-

Iba pa: 3C-SiC, uri-P, atbp.

-

-

-

SiCWaferPag-iimpake at Pagpapadala

2. T: Ano ang mga pangunahing bentahe ng SiC wafers kumpara sa silicon wafers?

A: Kung ikukumpara sa mga silicon wafer, ang mga SiC wafer ay nagbibigay-daan sa:

-

Mas mataas na operasyon ng boltahe(>1,200 V) na may mas mababang on-resistance.

-

Mas mataas na katatagan ng temperatura(>300 °C) at pinahusay na pamamahala ng init.

-

Mas mabilis na bilis ng paglipatna may mas mababang switching losses, na binabawasan ang paglamig sa antas ng sistema at laki sa mga power converter.

4. T: Anong mga karaniwang depekto ang nakakaapekto sa ani at pagganap ng SiC wafer?

A: Kabilang sa mga pangunahing depekto sa mga SiC wafer ang mga micropipe, basal plane dislocations (BPD), at mga gasgas sa ibabaw. Ang mga micropipe ay maaaring magdulot ng mapaminsalang pagkabigo ng aparato; ang mga BPD ay tumataas ang on-resistance sa paglipas ng panahon; at ang mga gasgas sa ibabaw ay humahantong sa pagbasag ng wafer o mahinang epitaxial growth. Samakatuwid, ang mahigpit na inspeksyon at pagpapagaan ng depekto ay mahalaga upang ma-maximize ang ani ng SiC wafer.

Oras ng pag-post: Hunyo-30-2025